芯片面积与性能的博弈 为何不轻易放大核心?

在探讨手机芯片性能提升的路径时,一个看似直接的想法是:为什么不通过增大芯片的核心面积来容纳更多晶体管,从而大幅提升性能呢?这背后涉及集成电路设计、制造、成本、功耗及用户体验等多维度的复杂权衡。

从设计与制造工艺的角度看,芯片面积并非可以无限扩大。现代手机芯片采用先进的半导体制造工艺(如3nm、5nm),在晶圆上刻蚀电路。晶圆的尺寸是固定的,单个芯片面积越大,单个晶圆上能产出的合格芯片数量就越少,这直接导致生产成本飙升。更重要的是,芯片面积增大后,在制造过程中出现缺陷的概率也随之增加,因为更大的面积意味着更有可能涵盖晶圆上的微小瑕疵,从而降低良品率。

功耗与散热是手机芯片设计的核心制约因素。芯片的功耗大致与晶体管数量成正比,面积增大意味着可以集成更多晶体管,但功耗也会急剧上升。手机作为移动设备,电池容量和散热空间极其有限。过高的功耗不仅会导致电池续航骤减,还会产生大量热量,若散热设计无法跟上,将引发芯片降频以保护硬件,反而导致性能不稳定甚至下降。因此,单纯增加面积而不解决功耗和散热问题,是得不偿失的。

从系统集成与尺寸限制考虑,手机内部空间寸土寸金。芯片面积增大,会挤占电池、摄像头、散热模组等其他关键部件的空间,影响整机设计的紧凑性与功能性。手机厂商需要在性能、续航、拍照、轻薄手感等多方面取得平衡,过大的芯片会打破这种平衡。

芯片设计及服务行业是如何在不显著增加面积的前提下提升性能的呢?主要路径包括:

- 制程工艺升级:通过缩小晶体管尺寸(如从7nm到5nm),在相同面积内集成更多晶体管,提升能效比。

- 架构创新:优化CPU、GPU、AI加速器等核心的微架构,提高每时钟周期指令执行数(IPC),让每个晶体管发挥更大效能。

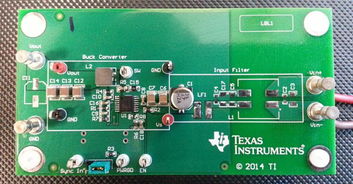

- 异构计算与专用单元:集成针对AI、影像、安全等任务的专用处理单元(如NPU、ISP),提升特定任务的能效,而非依赖通用核心的粗暴扩张。

- 先进封装技术:采用如2.5D/3D堆叠封装,在垂直方向而非水平方向扩展,实现更高密度集成,同时控制平面面积。

- 软硬件协同优化:通过算法、编译器、操作系统层面的深度优化,更高效地调度芯片资源。

在手机芯片领域,单纯“加大核心面积”并非提升性能的良策。它受到成本、良率、功耗、散热和整机设计的严格限制。现代芯片性能的飞跃,更多依赖于制程微缩、架构革新、异构整合与先进封装等技术的综合演进。芯片设计及服务公司的核心竞争力,正是在于在这些约束条件下,通过精巧的设计与系统级优化,实现性能、能效与成本的绝佳平衡,持续推动移动计算体验的边界。

如若转载,请注明出处:http://www.yiyunping.com/product/51.html

更新时间:2026-02-28 13:19:26